TWS耳機是與人體頻繁而又密切接觸的電子產品,其經常籠罩在靜電干擾(ESD)的“陰影”當中。

當靜電干擾(ESD)事件從TWS耳機的各個角落進入到芯片的電源、地、模擬輸入、數字輸出等引腳時,芯片將面臨著擊穿損壞、電源崩潰、時鐘紊亂、誤復位等災難性問題。因此,芯片系統的高可靠性設計對TWS耳機的品質保證變得尤為重要。

芯片系統的可靠性包括:系統長時間工作的穩定性,群脈沖、浪涌、ESD 條件下系統的穩定性以及電源體系、時鐘系統和復位電路等等的可靠性。

深圳銳盟半導體有限公司擁有可靠性設計的豐厚技術積累,擁有業界領先的高可靠性電路設計核心技術,在保護電路、電源體系、時鐘系統和復位電路等方方面面都擁有領先的專利技術。

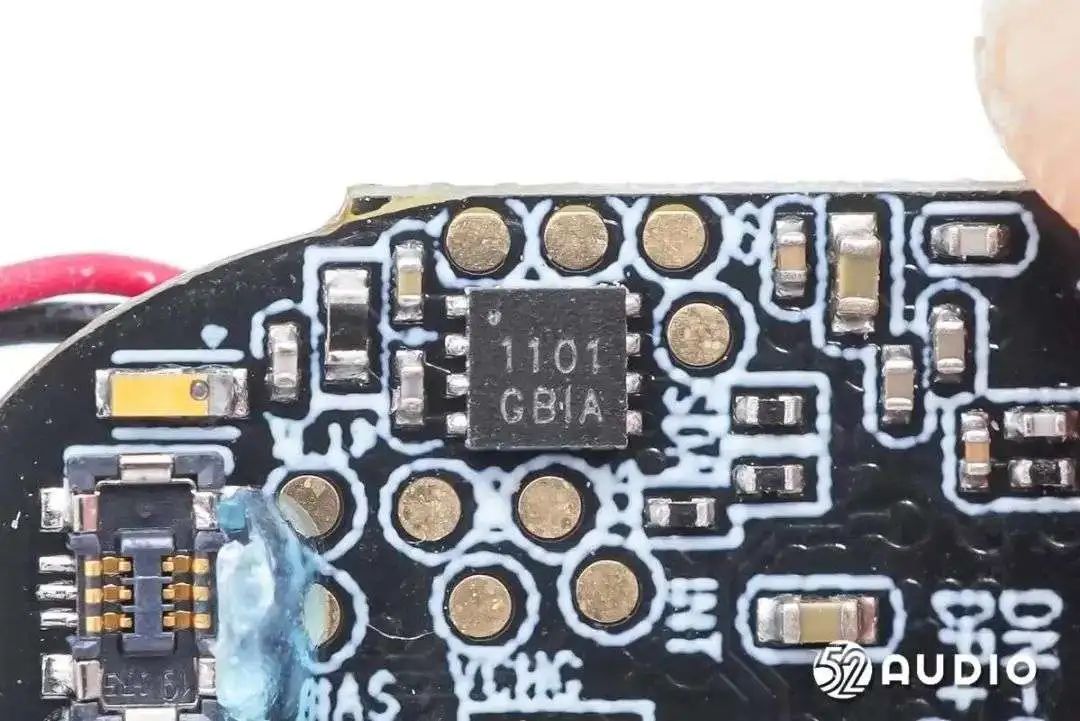

(1)擁有自主知識產權的CLAMP鉗位電路及其泄放電路,使得在HBM 8KV 的 ESD 和 4KV 的 EFT 等干擾事件下,芯片都能夠很好的泄放電源干擾,并保證時鐘、電源和復位電路不會誤觸發毛刺干擾。

(2)擁有高穩定性電源系統。銳盟半導體在芯片版圖電源的布局布線以及電源 PAD 的保護電路上都有豐富經驗,在 IO ESD 電路與內部電路的隔離和模數混合電路的抗串擾設計上,創造性優化了去耦電容結構并增加脈沖吸收電路,充分保證電源系統的穩定性。

(3)擁有高可靠性復位電路。TWS耳機由電池供電,當耳機組裝焊接電池過程中,電源線連接瞬間會由于焊接過程的振動接觸而發生us級的反復上電/掉電過程。銳盟半導體的芯片復位體系由上電復位和掉電復位兩部分組成,ns級別極速響應的復位電路能夠保障系統復位的可靠性。

在系統上電復位成功后,還能夠對外部干擾信號進行濾波,避免在強干擾條件下的誤復位。傳統的由模擬電路組成的復位電路,在上電過程中,會出現復位不良,如遇電源電壓不穩,系統反復上電,發生復位不良的概率更高。銳盟半導體創造性的采用了模擬與數字電路結合、混合遲滯濾波的方式,確保了復位電路的可靠性。

(4)擁有高穩定性時鐘系統。在群脈沖、ESD 等條件下,系統時鐘極易受到干擾,產生尖峰脈沖,影響系統的穩定性。銳盟半導體的專利技術能夠去除時鐘啟動過程的不穩定波形,并在時鐘信號進入logic電路之前,消除尖峰脈沖,進行濾波和整形,從而保障進入logic電路的時鐘具有穩定的頻率和占空比。

綜上所述,銳盟半導體在業界領先的高可靠性電路設計,將保證芯片系統能夠在電池上/下電、各種復雜而又頻繁的靜電干擾(ESD)中穩定工作,為TWS耳機安全可靠的運行保駕護航。

日期:2021-03-31

日期:2021-03-31

粵公網安備44030002001038

粵公網安備44030002001038